## Rapid Prototyping of Complex Micro-architectures through High-Level Synthesis

Sara Hoseininasab, Caroline Collange, Steven Derrien Inria, Univ Rennes, CNRS, IRISA, Rennes, France

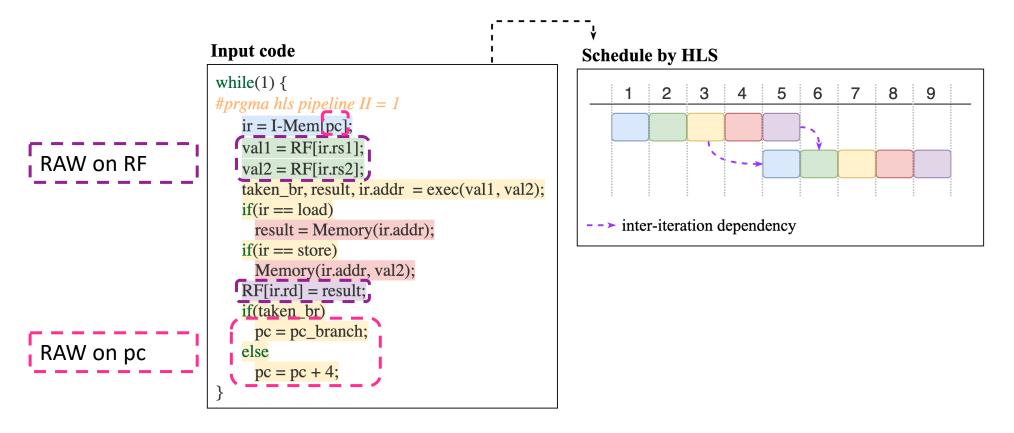

✓ Synthesizing a Single-threaded CPU simulator through HLS:

✓ II = 4 ----> HLS relies on static scheduling and considers worst-case scenarios

✓ How can achieve II = 1?

✓ To address this challenge, some works expose the pipeline stages in the simulator code and force HLS to follow the explicit scheduling [1]:

## An explicitly pipelined simulator

```

while(1) {

\#prgma\ hls\ pipeline\ II=1

writeback_tmp(memtowb);

memtowb_tmp = memory(extomem);

extomem_tmp = execute(dctoex);

dctoex_tmp = decode(fetodc);

fetodc_tmp = fetch();

/* Handling stalls */

if(!stall[fetch])

fetodc = fetodc_temp;

if(!stall[decode])

dctoex = dxtoex_temp;

```

## RTL in disguise!!

- ✓ Forces HLS to follow this schedule rather than relying on its automatic scheduling ---> not fully utilizing HLS capabilities

- ✓ Same level of complexity as RTL ---> not raising the level of abstraction

- Requires identification and handeling of pipeline stages and pipeline hazards

- ✓ Modifying the pipeline structure often requires a complete rewrite, making DSE difficult

Our approach: I will explain in my poster session how we exploit HLS features to synthesize complex micro-architectures without delving into RTL implementation.