#### https://fpga-ignite.github.io/

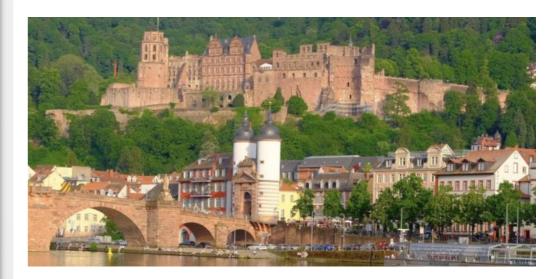

## FPGA IGNITE SUMMER SCHOOL 2024 Heidelberg University, August Sth to 9th

## **UNIVERSITÄT HEIDELBERG** ZUKUNFT SEIT 1386

## Our Venue

European Institute for Neuromorphic Computing (EINC) research building

**Electrons** — **Spiking Neuromorphic Hardware**

Photons — **Highly-integrated Neuromorphic Optics**

Atoms — **Ultracold Quantum Simulators**

Building tours will be available during the Hackathon

Gold Sponsor

**GEFÖRDERT VOM**

Bundesministerium für Bildung und Forschung

## Chip Sponsor

# efabless:

Bronce Sponsor

### Funding program "Design Instruments for Sovereign Chip Development with Open Source (DE:Sign)"

Program Management Agency VDI/VDE-IT for BMBF/Ref. 512 Electronics and Autonomous Driving; Supercomputing

#### VDI VDE IT

### GERMAN MICROELECTRONICS DESIGN INITIATIVE

- BMBF program for Chip Design Resources in Germany

- Start in 2022

Components of the Initiative (so far):

- Network "Chipdesign Germany"

- DE:Sign Funding for OpenSource Chip Design

- 15 projects, running May 2024 to April 2027

- BMBF Total Grant: 29.6 Mio. EUR

- Funded collaborations between Germany and Taiwan

- 6 current projects, new call out now!

© Alexander Limbach - AdobeStock

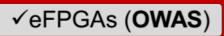

### DE:SIGN | R&D PROJECTS OPEN SOURCE EDA TOOLS

Talents: Student contest "Open Source Chip Design Challenge" (OCDCpro)

#### Analog design

✓ Text based design (ORDeC)✓ High frequency chips (DEMICO)

#### **Digital design**

✓Verifaction (OSVISE)

✓ FPGAs (FEntWumS) ✓ DRAM (DERAMSys)

✓ RISC-V (GATE-V)

✓ AI Hardware (EDAI)

Hardware security

✓HW architecture (ExViPaS)

✓HW security module (SIGN-HEP)

#### Novel technologies

✓ RFETs (ReDesign)✓ MEMS/ASIC (Meta-X)

✓ Radiation resistant HW (Flowspace)

✓ Packages/SiP (PASSIONATE)

3

### NEW FUNDING PROGRAM: RESEARCH ON MICROELECTRONICS WITH TAIWAN

® Svitlana - AdobeStock

- Funding for research collaborations in microelectronics between Germany and Taiwan

- R&D projects to research new approaches and methods on design tools, trustworthy chips and hardware for future applications, system integration and packaging

- Deadline pre-proposals: <u>15.09.2024</u>

- Networking event: <u>07.08.2024</u> (online) <u>https://www.elektronikforschung.de/design</u>

Further information: https://www.elektronikforschung.de/foerderung/bekanntmachungen/de-tw-kooperation https://www.elektronikforschung.de/foerderung/bekanntmachungen/foerderaufruf-2024-deutschland-taiwan

####

### CONTACT

Dr. Tina Tauchnitz

Program Management Agency on behalf of Federal Ministry of Education and Research Germany: VDI/VDE Innovation + Technik GmbH email: <u>designinitiative-me@vdivde-it.de</u> phone: +49 (0) 30 310078-3584

Dr. Korbinian Schreiber

#### Informationsblatt zur Bekanntmachung

#### "Forschungs- und Innovationszusammenarbeit mit Taiwan auf dem Gebiet der Mikroelektronik"

####

| Ansprechpartner: | Dr. Tina Tauchnitz (Dresden)<br>Dr. Korbinian Schreiber (Berlin)                                                             | Hotline: 030 310078-3584<br>E-Mail: <u>designinitiative-me@vdivde-it.de</u> |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                  | https://www.elektronikforschung.de/foerderung/bekanntmachungen/de-tw-kooperation                                             |                                                                             |  |  |  |  |

| Stichtag:        | 15. September 2024 (23:59 Uhr)                                                                                               |                                                                             |  |  |  |  |

| Text unter:      | www.bundesanzeiger.de vom 19.07.2024 (Rahmenrichtlinie)                                                                      |                                                                             |  |  |  |  |

|                  | https://www.elektronikforschung.de/foerderung/bekanntmachungen/foerderaufruf-2024-<br>deutschland-taiwan (Förderaufruf 2024) |                                                                             |  |  |  |  |

#### Ziel der Bekanntmachung

Mit dieser Bekanntmachung fördert das Bundesministerium für Bildung und Forschung (BMBF) in Zusammenarbeit mit dem National Science and Technology Council Taiwan (NSTC) in einem wettbewerblichen Verfahren FuE-Vorhaben mit Taiwan auf dem Gebiet der Mikroelektronik, um langfristige, kooperative Forschungsbeziehungen in der Mikroelektronik mit Taiwan zu schaffen. Gegenstand der Förderung sind grundsätzlich FuE-Aufwendungen deutscher Partner in vorwettbewerblichen, bilateralen FuE-Vorhaben zwischen Hochschulen und Forschungseinrichtungen an den Standorten Deutschland und Taiwan.

Fachlich-inhaltlich werden neue Forschungsansätze und -methoden innerhalb der gesamten Mikroelektronik gefördert. Der thematische Fokus innerhalb der Mikroelektronik wird mittels jährlicher Förderaufrufe gesetzt. Das NSTC wird zeitgleich entsprechende Förderaufrufe veröffentlichen. Für Vorhaben im Rahmen des Förderaufrufs 2024 müssen die geplanten Arbeiten in den FuE-Vorhaben in mindestens einem der folgenden Bereiche einschlägige Kerninnovationen hervorbringen und damit den aktuellen Stand der Technik deutlich übertreffen:

- Entwicklung und Erforschung von neuen Design-Werkzeugen und -Methoden der Entwurfsautomatisierung (electronic design automation, EDA) für souveräne Chipentwicklung entlang der gesamten Prozesskette, insbesondere EDA-Werkzeuge einschließlich Entwurfs-, Simulations- und Verifikationswerkzeuge, Prozess-Design-Kits (process development kit, PDK), Montage-Design-Kits (assembly development kits, ADK) und IP-Blöcken (intellectual property). Ein besonderer Fokus liegt auf quelloffenen EDA-Werkzeugen, PDKs/ADKs und IP-Blöcken. Die neu- oder weiterentwickelten Design-Werkzeuge sollen innovative Chip-/Systementwürfe einschließlich neuartiger Schaltungs-/Systemarchitekturen und -topologien, sowie neue Ansätze für die Heterointegration und Advanced Packaging kompakter Elektroniksysteme ermöglichen. Idealerweise und sofern möglich soll eine durchgängige parallele Hardware-Entwicklung vom Design bis zum fertigen Chip bzw. Elektroniksystem demonstriert werden.

- 2. Entwurf, Entwicklung und Erforschung von anwendungsspezifischen, maßgeschneiderten Mikrochips und vertrauenswürdiger Hardware für zukunftsweisende Anwendungen, insbesondere Beschleuniger, Spezialprozessoren und neuromorphe Chips für energieeffizientes Rechnen und KI-gestützte Datenverarbeitung im Edge-Computing, im

####

Autonomen Fahren, in der Robotik und für weitere Hochleistungsanwendungen; neuartige oder spezialisierte Mikroelektronik für Hochfrequenzanwendungen der Kommunikationstechnologie, z. B. 6G Telekommunikation, Silizium-Photonik, etc.; spezielle Mikroelektronik für Medizinanwendungen und intelligente Sensorik im Bereich Smart Health; dedizierte Mikroelektronik für den Ausbau der Quantentechnologien, z. B. Kryoelektronik, robuste Quantenelektronik-Hardware, etc.

Erforschung und Erprobung innovativer Ansätze und Konzepte der Systemintegration und der Aufbau- und Verbindungstechnik f

ür hochintegrierte Elektronik, insbesondere neuartige Interconnects, Chiplets und 2.5D/3D-Elektroniksysteme f

ür Hochleistungsanwendungen (z. B. Daten

übertragung mit hoher

Übertragungsrate, Bandbreite, Frequenz).

Die Arbeiten in den FuE-Vorhaben sollen vor allem Chip- und Systeminnovationen mit hoher wissenschaftlicher und zukünftig wirtschaftlicher Relevanz vorantreiben. Die Vorhaben sollen einen klaren Bezug zur Entwicklung von Mikroelektronikhardware aufweisen.

Bei der Planung der Vorhaben sollen zudem die folgenden Aspekte berücksichtigt und adressiert werden:

(i) detailliertes Konzept für einen gegenseitigen Studierendenaustausch (in der Regel 1 Aufenthalt pro Studierenden und Projekt für eine Dauer von 6 Monaten), (ii) Vertrauenswürdigkeit durch Transparenz und gute wissenschaftliche Praxis, (iii) wirksame Einbindung individueller Forschungsexpertise und Vorarbeiten, (iv) starke Interaktionen, intensiver Austausch und wissenschaftliche Vernetzung, sowie (v) Identifizierung von konkreten Anwendungsperspektiven und Verwertungspotenzialen sowie Konzepte zum Transfer der Ergebnisse in die wirtschaftliche Nutzung.

Die Projektskizzen stehen im Wettbewerb untereinander und werden nach den folgenden Kriterien bewertet:

- fachlicher Bezug zur Förderrichtlinie bzw. zum Förderaufruf:

- Beitrag zu Aufbau und Festigung von Kooperationspartnerschaften zwischen Deutschland und Taiwan in innovativen Forschungsfeldern,

- Einbindung und Stärkung von Nachwuchsgruppen, Berücksichtigung von Aus- und Weiterbildungsaspekten,

- technische, wirtschaftliche und gesellschaftliche Bedeutung einschließlich Aspekte der Nachhaltigkeit,

- wissenschaftlich-technische Qualität des Lösungsansatzes, Neuheit, Innovationshöhe und Risiken des Konzepts,

- Projektstruktur:

- Qualität und Angemessenheit der Arbeits-, Finanzierungs- und Ressourcenplanung,

- Kompetenz und Ausgewogenheit des Projektkonsortiums im Sinne der Förderrichtlinie,

- Verwertungskonzept und Verwertungspotenzial, Beitrag zur Stärkung der technologischen Souveränität am Standort Deutschland.

**Verfahren:** Elektronische Skizzeneinreichung unter <u>https://foerderportal.bund.de/easyonline</u> - BMBF; "Forschungs- und Innovationszusammenarbeit mit Taiwan auf dem Gebiet der Mikroelektronik"

| U | B | E | R | U | N | S |  |  |

|---|---|---|---|---|---|---|--|--|

|   |   |   |   |   |   |   |  |  |

AKTUELLES

ARBEITSGRUPPEN

HOCHSCHULALLIANZ

NACHWUCHS

KONTAKT

#### AUFTAKTVERANSTALTUNG

Gemeinsam Innovationen schaffen: Auftaktveranstaltung des Netzwerks Chipdesign Germany mit Networking-Events

| Zum | Event |  |

|-----|-------|--|

#### **CHIPDESIGN GERMANY**

#### Das Netzwerk für Chipdesign in Deutschland

Das Chipdesign ist der wesentliche Schritt, um Mikroelektronik für die eigenen Produkte und Anwendungen zu entwerfen. Über Kompetenz im Chipdesign lässt sich die Innovations- und Wettbewerbsfähigkeit Deutschlands stärken und ein Zugewinn an technologischer Souveränität in Europa erzielen. Um dieses Potenzial zu heben, soll das deutsche und europäische Chipdesign-Ökosystem ausgebaut werden. Dazu wurde die Designinitiative Mikroelektronik gestartet, die sich auf die folgenden vier Schwerpunkte stützt: ein starkes Netzwerk als zentrale Austauschplattform, Aus- und Weiterbildung von Talenten und Fachkräften, die Durchführung von Verbundforschungsprojekten zur Stärkung der Design-Fähigkeiten sowie der Ausbau und die Stärkung von Forschungsstrukturen.

Das Netzwerk Chipdesign Germany ist eine Plattform in Deutschland für den vorwettbewerblichen, offenen Austausch zwischen allen am Chipdesign beteiligten Akteuren. Es sollen geeignete Kooperationsstrukturen, Beratungsleistungen für Start-up und KMU sowie neue Geschäftsmodelle entwickelt werden.

#### **MITGLIED WERDEN**

Virtually everything we use and build is or will be...

### Day 1 (Monday, August 5th)

- 9:30 Reception and refreshments

- 10:00 10:30 FPGA Ignite 2024 opening and program introduction

- 10:30 11:30 Poster Pitches

- 11:30 12:00 Poster networking coffee (~25 Posters) (click here for more details)

- 12:00 12:45 Hackathon intro (including team forming)

- 12:45 14:00 Lunch

- **14:00 14:45** FOSSi Foundation + open source chip design <u>Philipp Wagner</u>

- 14:45 15:10 Coffee break

- **15:10 15:55** Keynote Prof. <u>Guy-Lemieux</u>, University of British Columbia, CA

- **16:00** Hike to <u>Neuburg Abbey</u> (over the <u>Philosophers'</u> <u>Walk</u>) and dinner (18:00) at <u>Klostergarten</u>

## Day 2 (Tueday, August 6th)

**9:00 – 10:30** Kickoff (15 min, <u>Guy Lemieux</u>) & cocotb (<u>Marc Andre</u>)

- 10:30 11:00 Coffee break

- 11:00 12:30 cocotb (Marc Andre)

- 12:30 13:30 Lunch

- **13:30 15:00** RISC-V customization Basics (<u>Guy</u> <u>Lemieux</u> and <u>Stefan Wallentowitz</u>)

- 15:00 15:30 Coffee break

- **15:30 17:00** Testing Instruction Extensions with cocotb & icarus (<u>Stefan Wallentowitz</u> and <u>Philipp Wagner</u>)

- **18:30** Dinner at Zeughaus-Mensa, later: guided city tour.

### Day 3 (Wednesday, August 7th)

**9:00 – 10:30** RISC-V Customization - Software Analysis Tooling (identify custom instruction), Extending LLVM and Cores (<u>Stefan Wallentowitz</u>)

10:30 - 11:00 Coffee break

**11:00 – 12:30** Reconfigurable Instruction Set Extensions using FABulous eFPGAs - when and how (introduction and hands-on tutorial) (<u>Dirk Koch</u>)

12:30 - 13:30 Lunch

**13:30 – 15:00** Boosting the efficiency of RISC-V cores: Fine-grain multi-threading and custom instructions, from concepts to implementation (<u>Riadh Ben Abdelhamid</u>)

15:00 – 15:30 Coffee break

**15:30 – 17:00** Boosting the efficiency of RISC-V cores: Fine-grain multi-threading and custom instructions, from concepts to implementation (<u>Riadh Ben Abdelhamid</u>)

19:00 Surprise Reception

### Day 4 (Thursday, August 8th)

#### **Hackathon Day 1**

- 9:00 10:00 OpenLane Intro (Nguyen Dao)

- 10:30 11:00 Coffee break

- 11:00 12:30 Hackathon

- 12:30 13:30 Lunch

- 13:30 Hackathon

### Day 5 (Friday, August 9th)

#### Hackathon Day 2

9:00 - 16:30 Hackathon

16:30 Best Project Award and Wrap-Up

### Hackathon

### Hackathon

Fr. 16:30 – 17:00 Best Project Award

#### Judges

**Dr. Christian Färber** (Intel)

**Dr. Johannes Schemmel** (Heidelberg University)

## FPGA Ignite 2024 is Hybrid!

We accepted

60 in-person registrations

80 online registrations

+ additional viewers on

a YouTube live stream

- In-person attendees are from:

- Germany (obviously)

- UK

- China

- Italy

- Pakistan

- Bangladesh

- Turkey

- Hungary

- India

- Greece

- Netherlands

- Romania

...and many more online!

- Morocco

- Egypt

- Bosnia & Herzegovina

- Lebanon

- Malaysia

## FPGA Ignite 2024 is Hybrid!

- We are using Zoom (the daily links had been shared with you by email)

- Stay muted

- Online Attendees use the chat function

for questions (most reliable)

- In-person attendees can use Zoom in the case that slides are difficult to read

- For the poster session (today)

- There is a breakout room (in Zoom) for each poster (the poster numbers match the breakout rooms)

- Online posters will be presented on the Computers in the back (they have webcams and headsets to talk to people)

## FPGA Ignite 2024 is Hybrid!

- For the labs Tuesday/Wednesday:

- Lectures are shown in the main room

- Each physical attendee will join the breakout room associated with the seat ID (its written on your table)

- 1 2 online attendees will body up with one physical attendee

If audio is not possible, use chat function

Hackathon instructions follow...

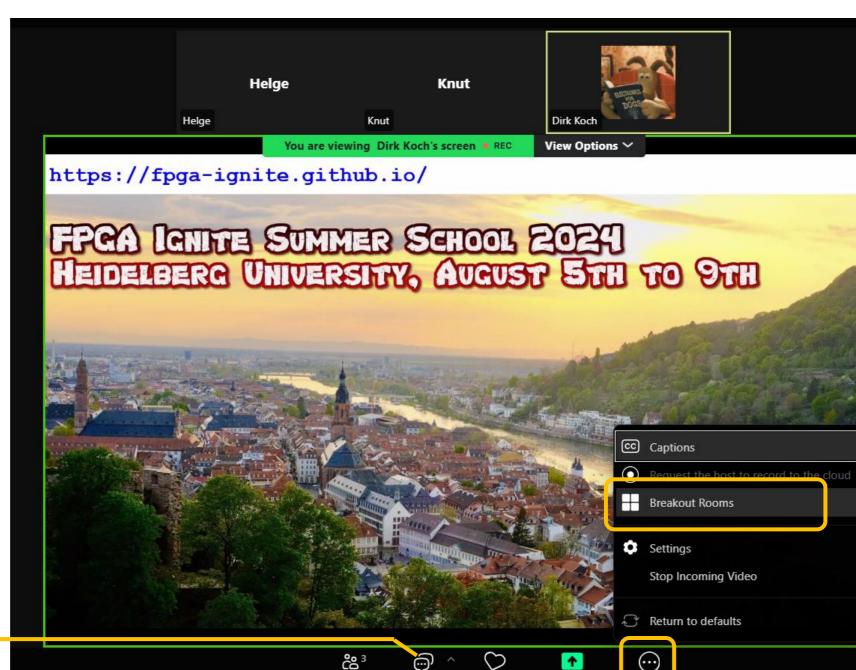

## Using Zoom

When we open the Breakout Rooms, click

and follow to

Breakout Rooms

Some clients may show the breakout room icon (makes it easier)

For questions use

Chat in Main Room

Share Screen

## Using Zoom

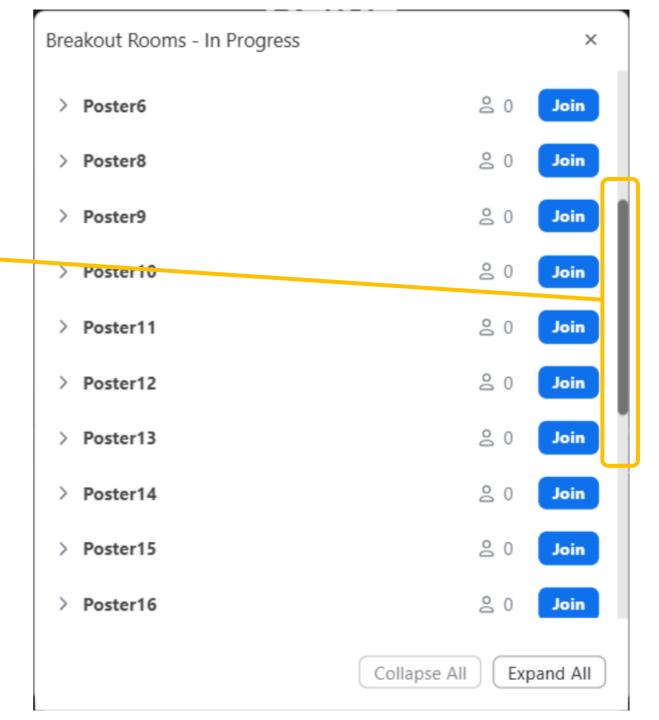

- Pick your Breakout Room with

- The slider is not always shown correctly but you can hoover along the right border of that menu and slide up/down (you may also try "Expand All")

- Mon: 25 Poster Breakout Rooms

- Tue/Thu: 60 Lab Breakout Rooms (again: for one physical and 1 or 2 online participants)

## Using Zoom

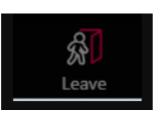

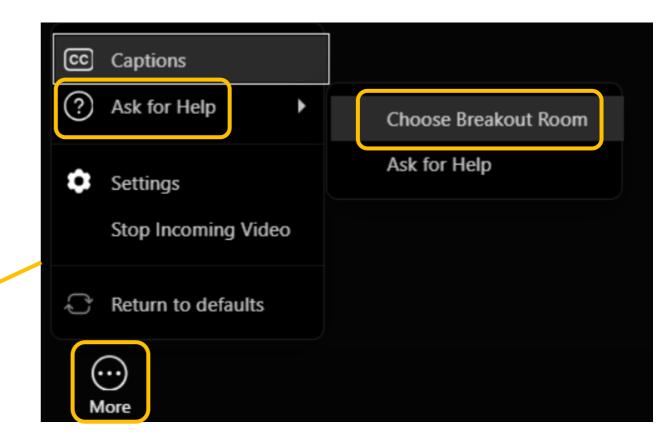

#### **Changing Breakout Rooms**

- Needed by online participants during the poster session

- Either click Leave (bottom right)

to go back into the main room from where you can join another B. Room

Or click on 1) More More

Go up to 2) Ask For Help

and go on 3) Choose Breakout Room

#### https://fpga-ignite.github.io/

### FPGA IGNITE SUMMER SCHOOL 2024 Heidelberg University, August Sth to 9th