# **OpenLane Tutorial - Hardening the Core**

The chip core would usually have other macros inside it.

## **Step 1:** Starting the OpenLane environment

Just run the following commands to enter the OpenLane environment (from the installed location of OpenLane)

cd Openlane/ make mount

# **Step 2:** Creating new designs

The following command creates a new configuration file for your design:

./flow.tcl -design <design name> -init\_design\_config -add\_to\_designs

This will create the following directory structure:

## **Step 3:** Create the RTL files

You need to create or copy the RTL files (including black-box). The recommended location for files is designs/<design name>/src/.v

## **Step 4:** Give the parameter configuration

You need to set the following environment variables in your configuration file for the chip core:

VERILOG\_FILES

VERILOG\_FILES\_BLACKBOX

EXTRA\_LEFS

EXTRA\_LIBS

EXTRA\_GDS\_FILES

SYNTH\_READ\_BLACKBOX\_LIB

MACRO\_PLACEMENT\_CFG

## **Step 5:** Run the flow on the macro design

Finally, run OpenLane. flow.tcl is the entry point for OpenLane. The command needs to be run from inside the environment of OpenLane as described in quick start.

```

./flow.tcl -design <design name> -tag full_guide —overwrite

```

## **Step 6:** Analyzing the flow generated files

You can open the interactive view using the following commands:

```

./flow.tcl -design <design name> -tag full_guide -interactive

package require openlane

run_synthesis

run_floorplan

run_placement

run_cts

run_routing

run_magic

run_magic

run_magic_spice_export

run_magic_drc

run_lvs

run_antenna_check

or_gui

```

The above commands can also be written in a file and passed to flow.tcl:

```

./flow.tcl –interactive –file <file>

```

## **Step 7:** Viewing of final layout

The following command generates a new gds or lef view for your design: klayout designs/<design name>/runs/full\_guide/results/final/gds or lef (or)

magic designs/<design name>/runs/full\_guide/results/final/gds or lef

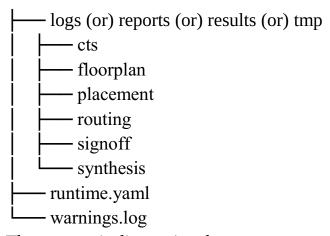

## **Each run has following structure:**

There are 4 directories logs reports results and tmp. In each of these directories, there are multiple directories. Directories are named according to the stage they belong to.

Finally output of OpenLane can be found in

designs/<design name>/runs/full\_guide/results/final

# **Example - DSP Tile:**

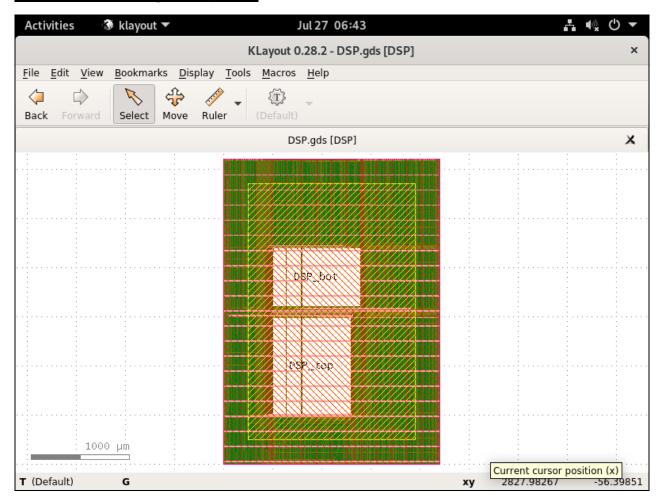

## **Configuration Variables:**

```

Activities

Text Editor ▼

Jul 27 06:48

*config.json

Open

⊞

~/sample/OpenLane/designs/dsptile1

2

"DESIGN NAME"

: "DSP",

: "dir::src/DSP.v",

"VERILOG FILES"

3

"SYNTH_READ_BLACKBOX_LIB"

: "true",

4

: "UserCLK",

"CLOCK PORT"

5

: "10.0",

6

"CLOCK PERIOD"

: "0 0 2200 3100",

7

"DIE AREA"

: "absolute",

8

"FP SIZING"

"FP ASPECT RATIO"

9

10

"STA REPORT POWER"

: "0",

: "1",

11

"SYNTH NO FLAT"

"QUIT ON SETUP_VIOLATIONS" : "0",

12

"MACRO_PLACEMENT_CFG" : "dir::macro_placement.cfg",

13

"EXTRA_LEFS" : ["dir::lef/DSP_bot.lef", "dir::lef/DSP_top.lef"],

"EXTRA_GDS_FILES" : ["dir::gds/DSP_bot.gds", "dir::gds/DSP_top.gds"],

"VERILOG_FILES_BLACKBOX" : ["dir::src/DSP_top.v", "dir::src/DSP_bot.v"]

14

15

16

17

18

```

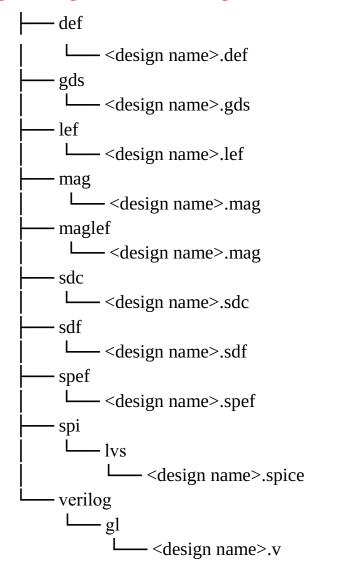

#### **GDS View using KLayout:**

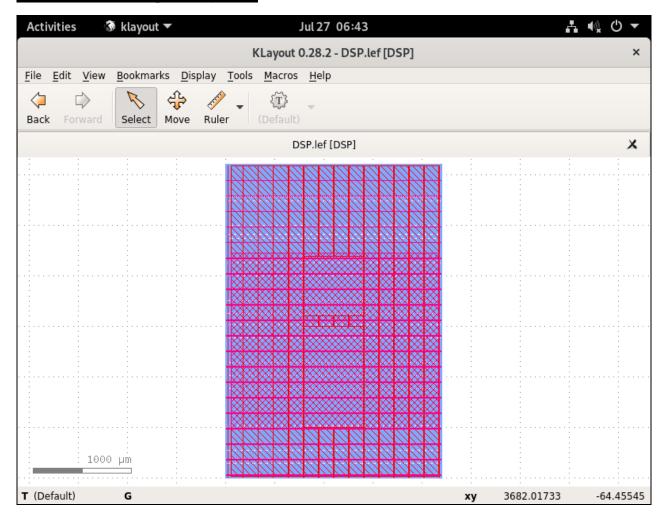

## **LEF View using KLayout:**